# fpgaemu Release 0.1

**Chadmond Wu**

May 06, 2021

# HARDWARE BASICS

| 1 | FPGA Review and Emulation Overview                                                                                                                                                                                                                                                      | 3                                             |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   | .2       What is an FPGA anyways?         .3       What's Inside an FPGA?                                                                                                                                                                                                               | 3<br>4<br>7<br>11                             |

|   | .5 Quick Definitions and Acronyms 1                                                                                                                                                                                                                                                     | 15<br>15                                      |

| 2 | 2.1       The AXI Protocol       1         2.2       AXI Reads and Writes       1         2.3       AXI4 Connections and Channels       1         2.4       AXI Interconnect vs. SmartConnect       2         2.5       AXI Verification IP       2                                     | 17<br>17<br>18<br>23<br>27<br>27              |

| 3 | B.1       Peripheral Component Interconnect       2         B.2       PCI Overview and Background       3                                                                                                                                                                               | <b>29</b><br>30                               |

| 4 | 4.1       What is RAM?       3         4.2       Different Types of RAM       3         4.3       SRAM       3         4.4       DRAM       3         4.5       The DDR SDRAM Protocol       3                                                                                          | <b>33</b><br>33<br>35<br>35<br>36<br>37<br>39 |

| 5 | 5.1       Clocks and Clock Conversion       4         5.2       Clock Tree       4         5.3       Multiple Clocks in an FPGA       4         5.4       Propagation Delay       4         5.5       Setup and Hold FF Time       4         5.6       Metastability Prevention       4 | <b>41</b><br>41<br>41<br>42<br>42<br>42       |

|   |                                                                                                                                                                                                                                                                                         |                                               |

|    | 6.4                                  | Linux Kernel Modules       45         Transferring Data Within the Kernel       46         References       46                                                                                                                                               |

|----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | 7.1                                  | /Bridge for PCIe Drivers Overview       47         The PCIe DMA Driver       47         Accessing and Building the Xilinx Driver       47                                                                                                                    |

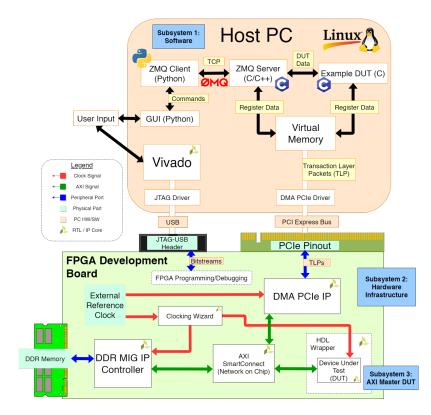

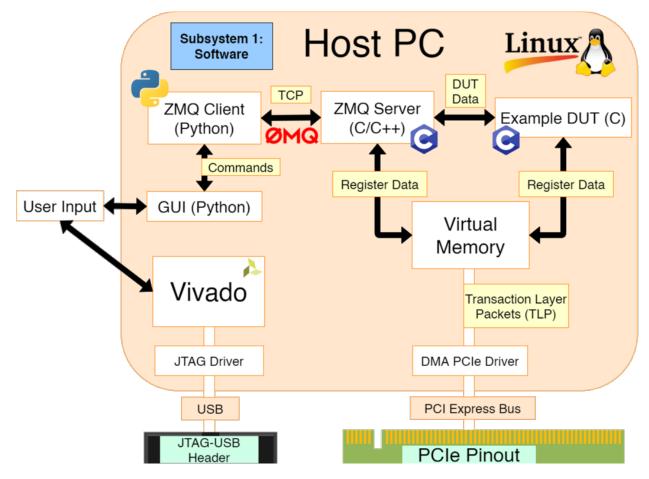

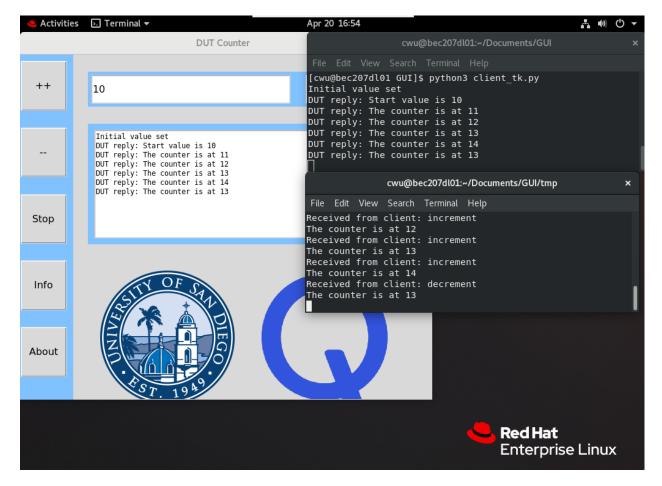

| 8  | 8.1<br>8.2                           | ing a User-Friendly DUT GUI49What is a GUI?49System Overview50Environment Setup51                                                                                                                                                                            |

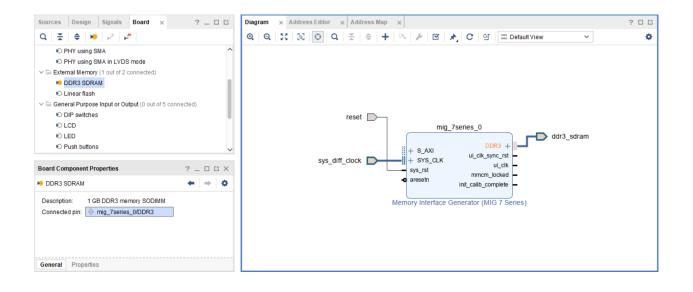

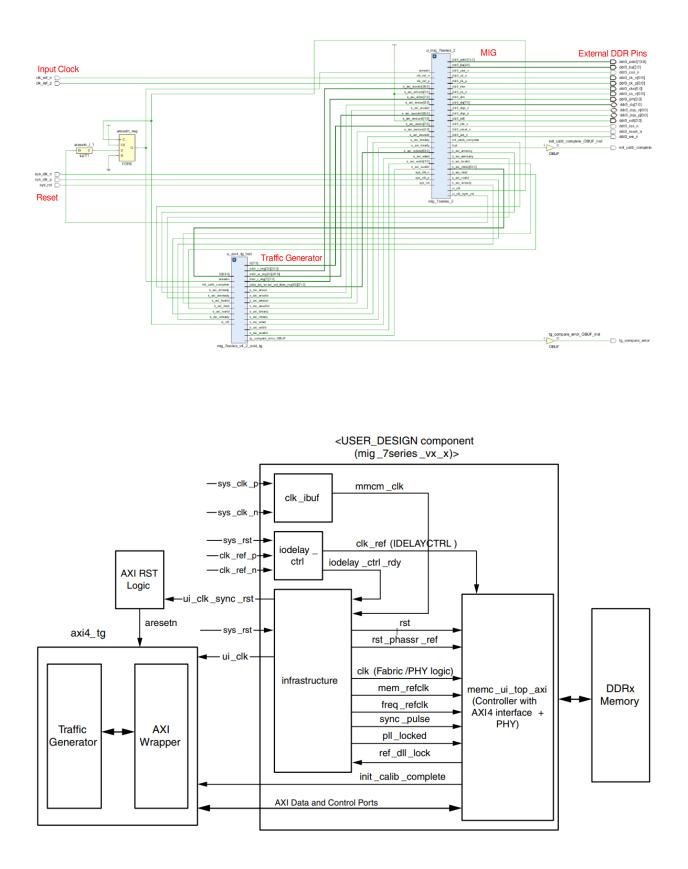

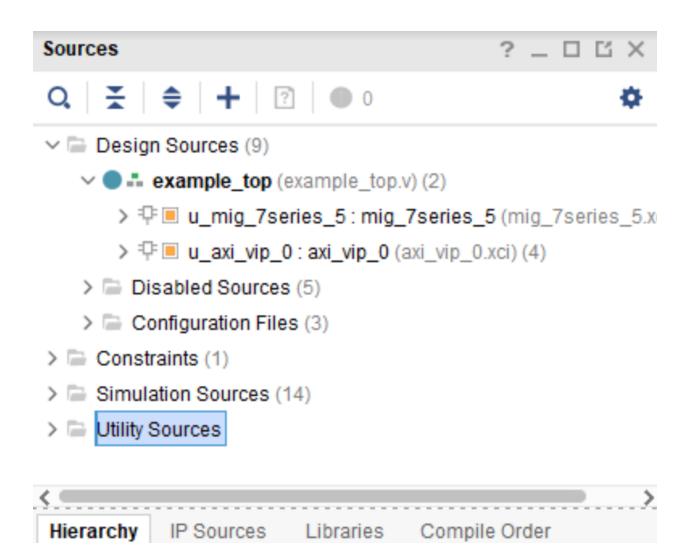

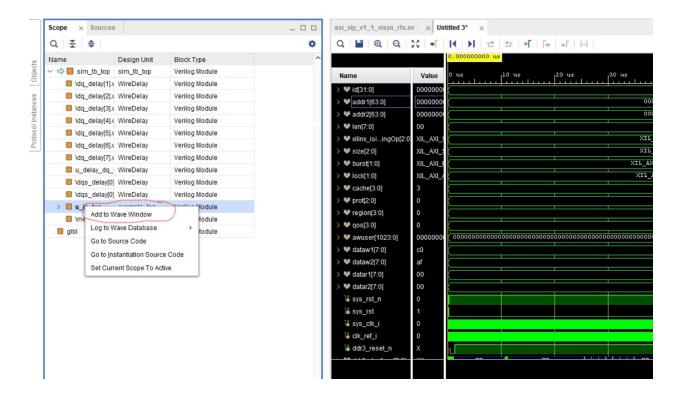

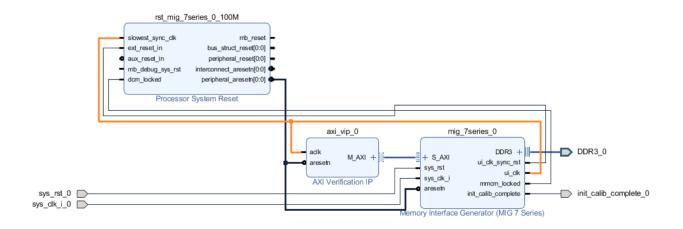

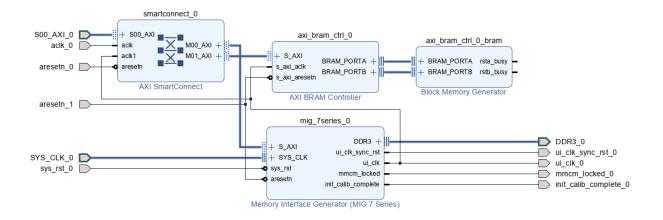

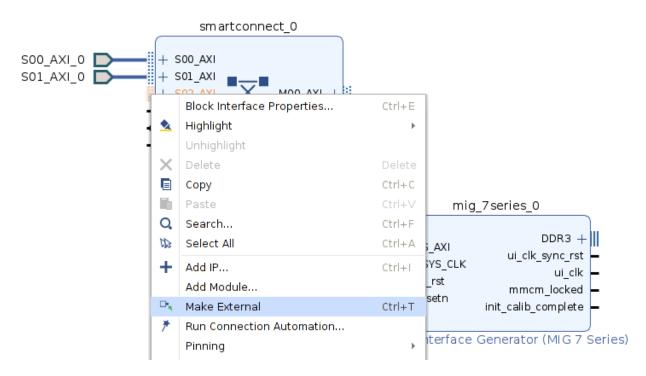

| 9  | 9.1<br>9.2<br>9.3<br>9.4             | 7 Series IP Overview55Customizing the IP55Simulating the Example Design57Simulating Read/Writes with AXI VIP59Connecting the MIG to a Custom Design66Connecting the MIG to Two AXI Master VIPs using AXI SmartConnect68                                      |

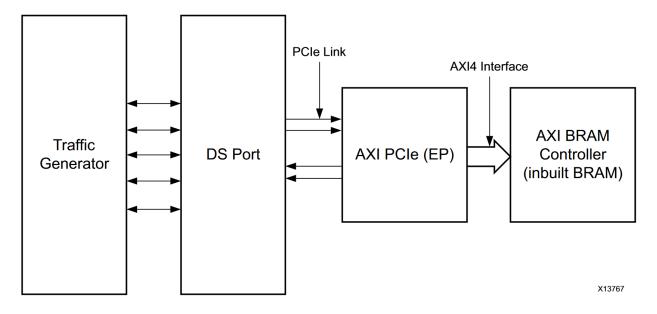

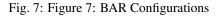

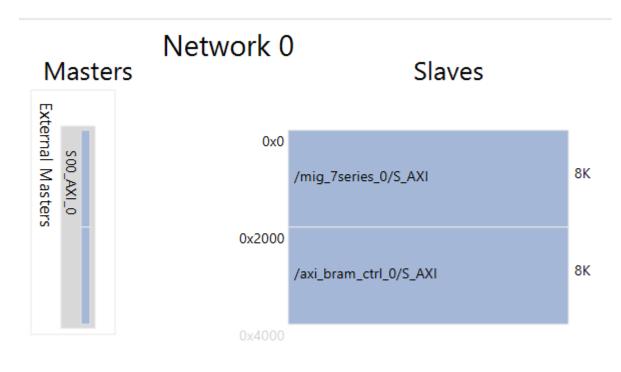

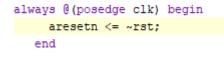

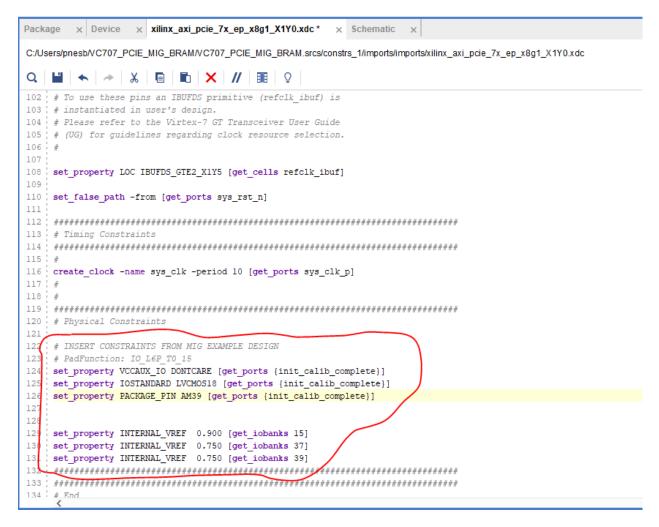

| 10 | 10.1<br>10.2<br>10.3<br>10.4         | AM to PCIe IP Overview77Customizing the IP77Simulating the Example Design77Example IP Block Diagram79Replacing the BRAM with DDR MIG in Example Design80Simulating the AXI MM PCIe MIG Example Design91                                                      |

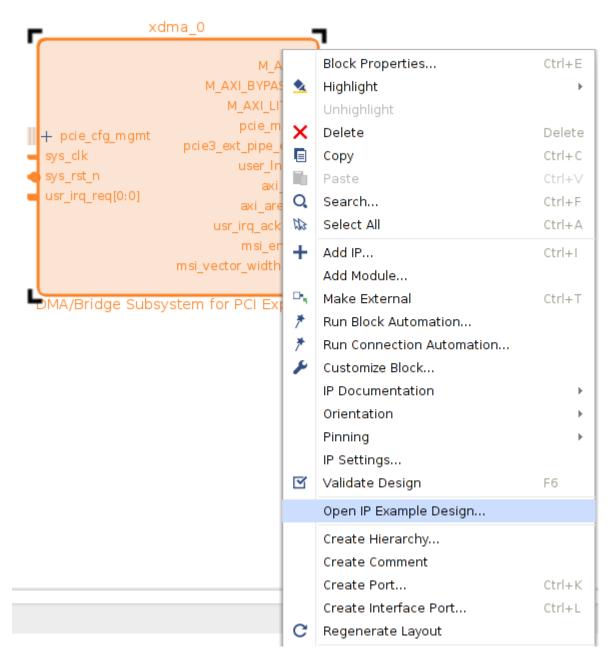

| 11 | 11.1<br>11.2<br>11.3                 | Bridge for PCIe IP Overview95DMA IP Overview95The DMA Protocol95Configuring the DMA IP97Additional Resources103                                                                                                                                              |

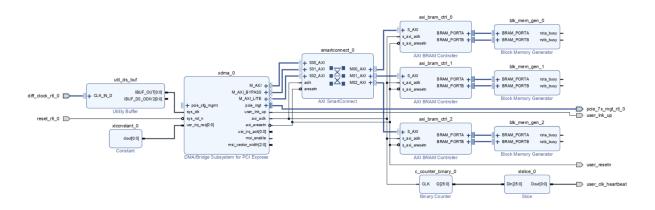

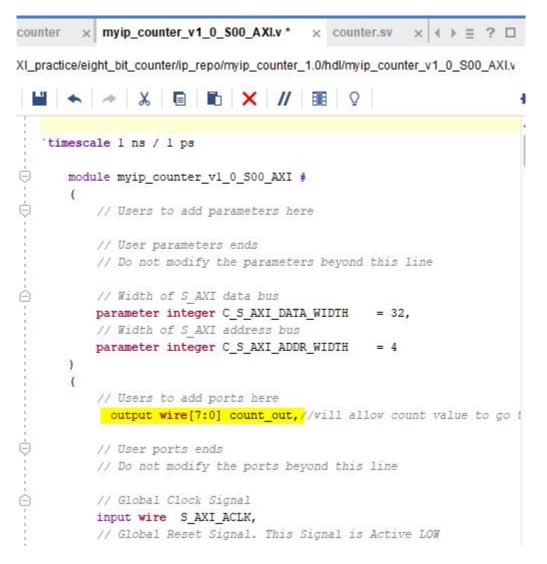

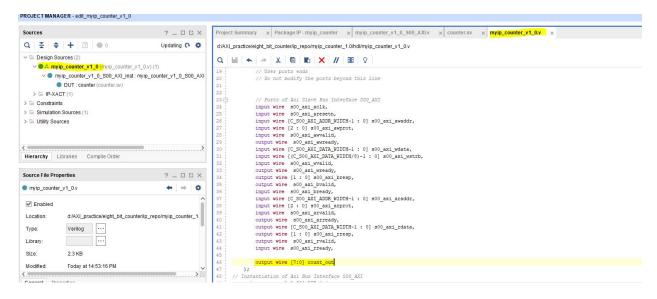

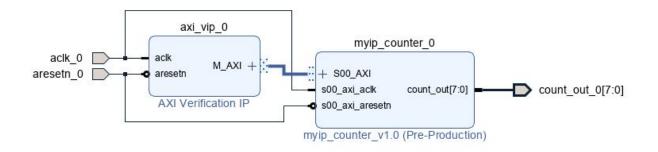

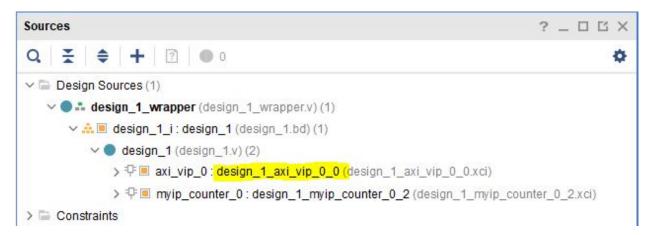

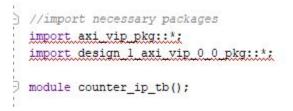

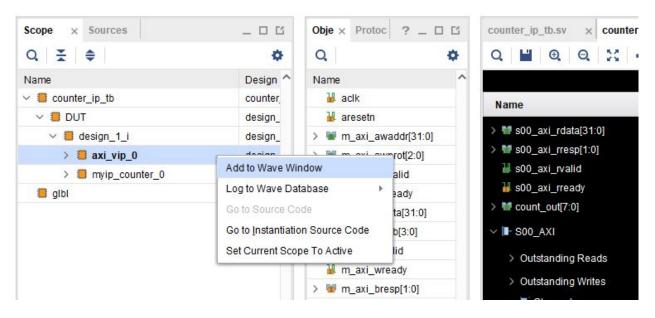

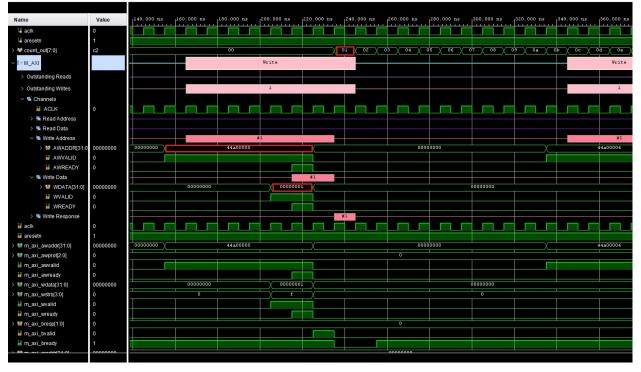

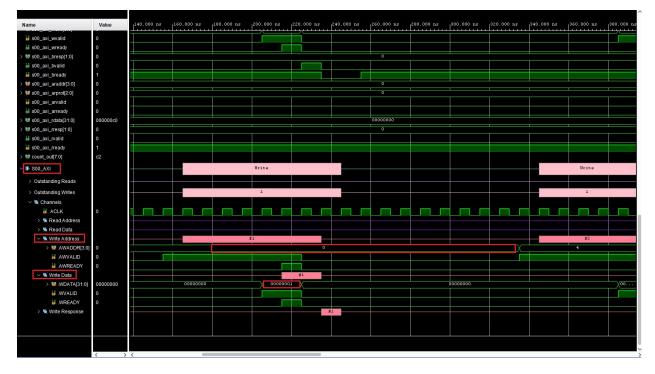

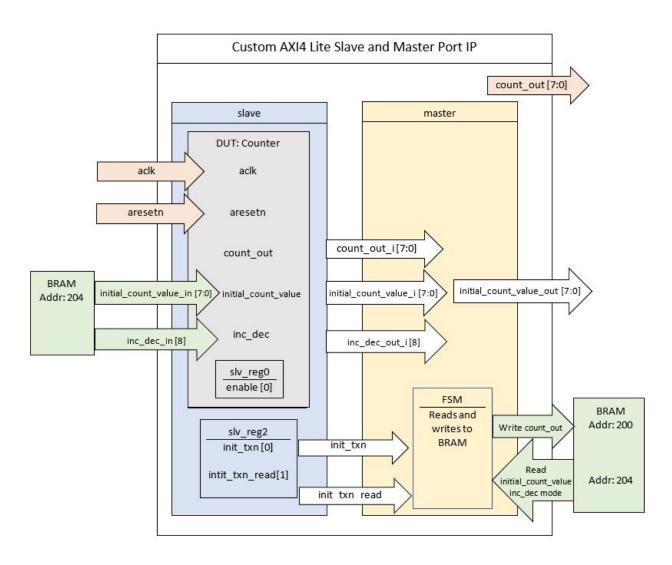

| 12 | 12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ing a Custom AXI IP Core105Packaging Custom IP105A Simple 8-Bit Counter105Packaging a Custom AXI4Lite IP109Adding a Custom AXI IP to a Design114Creating a Testbench for a Custom DUT116Interpreting Simulation Waveforms For a Custom DUT120                |

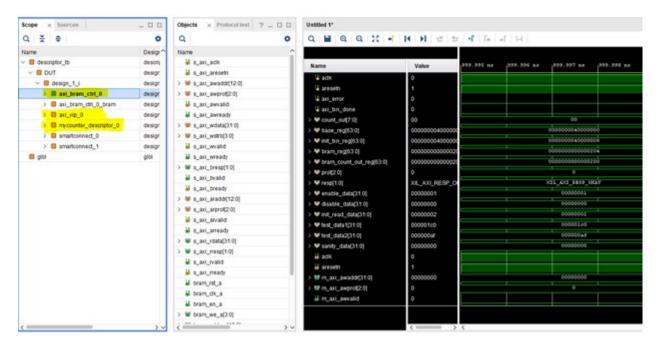

| 13 | 13.1<br>13.2<br>13.3<br>13.4         | ing an Advanced Custom AXI Descriptor IP123Features of Advanced DUT123Editing the Descriptor Counter IP125Creating the Master DUT Simulation Environment140Testbench for a Master Custom DUT140Simulating the Master Custom DUT141                           |

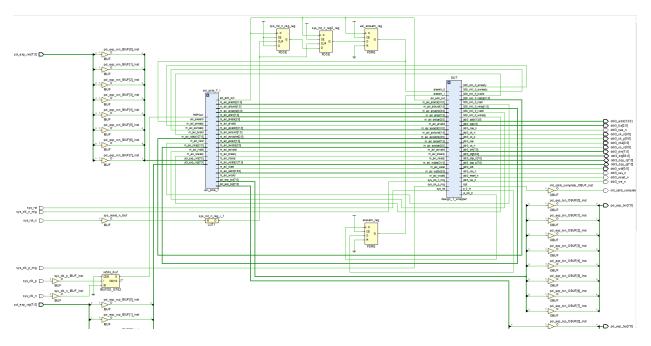

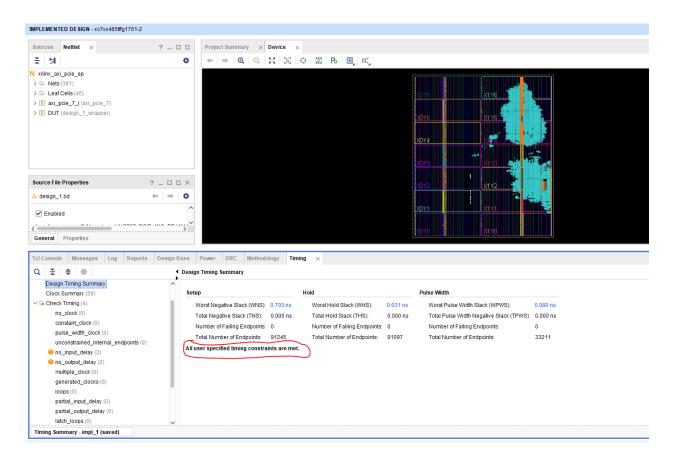

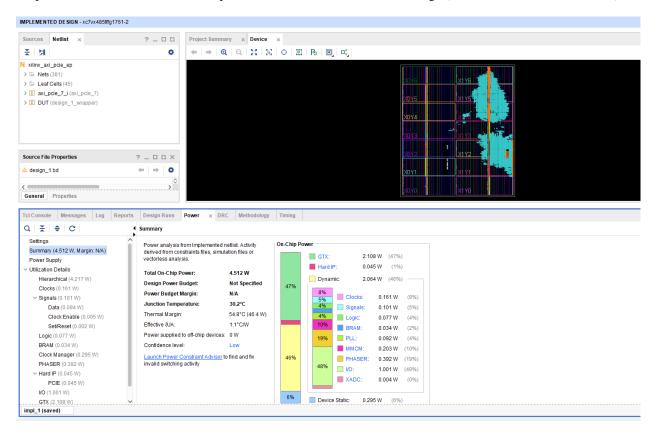

| 14 | 14.1<br>14.2<br>14.3<br>14.4         | ing a Basic Simulation Environment (VC707)143Generating PCIe and MIG Example Designs143Creating the Block Diagram146Connecting it All Together149Modifying and Running the Simulation153Checking Timing, Viewing Power Reports, Monitoring I/O Placement:158 |

| 15 | Building an Emulation Environment (without a Board)15.1Project Start (Building the Block Diagram) | <b>167</b><br>167 |

|----|---------------------------------------------------------------------------------------------------|-------------------|

| 16 | Project Summary         16.1       Project Abstract         16.2       Project Background         |                   |

| 17 | Additional Resources         17.1 Tutorials                                                       | <b>173</b><br>173 |

| 18 | Indices and tables         18.1       Acknowledgements                                            | <b>175</b><br>175 |

Note: You can find a brief summary of this project here and don't forget to check out our GitHub repo.

Important: New to FPGAs or just need a refresher? Jump here first!

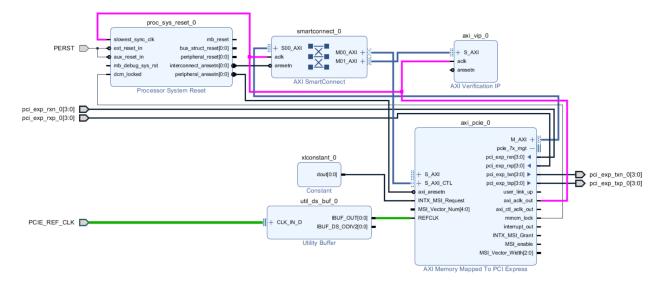

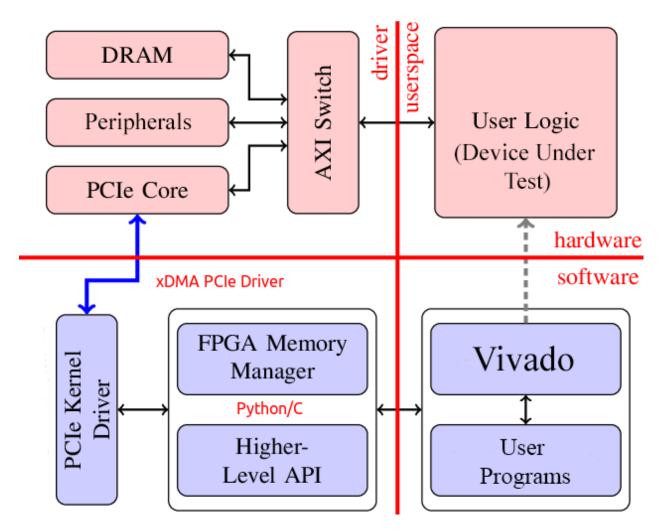

Fig. 1: Complete Block Diagram of FPGA Board

#### CHAPTER

# FPGA REVIEW AND EMULATION OVERVIEW

**Important:** This section is intended for FPGA and digital design beginners, although some intermediate concepts are briefly discussed.

# **1.1 A One Minute Introduction to FPGAs**

This fantastic quick video from Charles Clayton outlines the very basics of an FPGA. If you do not know what an FPGA is, start here before moving on.

Still confused? Here is a more approachable example that may help:

Imagine you had a box of USB sticks to sell, where each stick performs some task, whether it is counting from one to ten, transferring some songs to the hard drive, or even running another smaller computer. Because we hope to sell them, we should test every single stick (what we will refer to as a *device under test*) as much as possible for maximum compatibility to avoid any future errors or refunds. But, considering how many computers there are in the world, it is almost impossible to verify that every stick will work on every laptop or desktop aside from buying and testing on each one individually. The price for failure is high too, as a broken USB stick could potentially damage a user's computer, leading to an expensive safety recall.

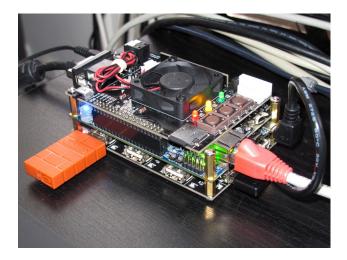

Now imagine if you had access to a special computer called an emulation evaluation board. From the outside, it is like any other computer, as the board also has USB, Ethernet, and other standard peripherals. However, at the heart of the board is what is known as an *FPGA*, a special kind of chip that can replicate/emulate every other computer in existence. Although a little clunky and hard to use, this FPGA means that you can now rest assured knowing that your USB sticks can be fully tested on every possible configuration before being sold. Not to mention, the board only needs to be set up once as an *emulation environment* before you're able to easily swap in and out DUTs for testing. Not bad, right?

Ready for a (slightly) technical deep dive? Read on for more details.

Fig. 1: A MiSTer board with Cyclone V FPGA

# 1.2 What is an FPGA anyways?

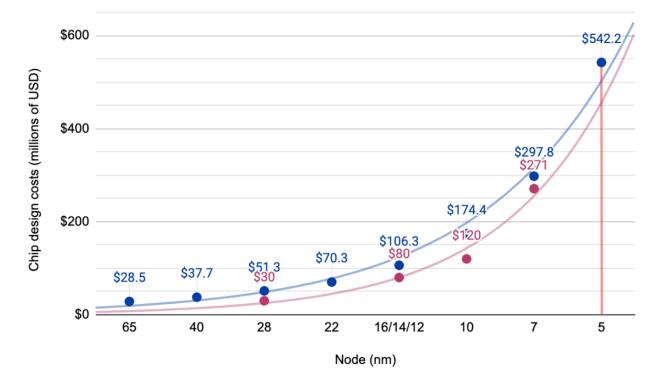

In 2020, Apple unveiled their newest computer chip, the M1, as the first 5nm processor for their range of Macintosh computers. As their very first in-house designed system on a chip, or **SoC**, the process of creating the M1 and other competitors like the Qualcomm Snapdragon 888 was very expensive, with costs reaching into the hundreds of millions of US dollars.

As an SoC iterates through each design and manufacturing step, the harder (and more expensive) it becomes to correct any errors. Think of a nightmare scenario where a manufacturer is forced to recall every single smartphone and computer due to a fatal bug with the CPU that was never caught (this happened to Intel and their Pentium processors in 1994!) This is where an FPGA becomes extremely useful.

Field programmable gate arrays or **FPGAs** are integrated circuits (a set of circuits layered within semiconductor material like silicon, also known as chips) designed to be configured by a customer or designer after manufacturing. With FPGAs, a designer can program features, adapt to environment and regulatory changes, and reconfigure hardware even in the field - hence the term *field programmable*. An FPGA contains programmable logic elements (LEs) that either act as basic logic gates or connect to perform complex actions as logic blocks. From a top-level perspective, FPGAs consist mostly of configurable memory, high speed I/O, logic blocks, and routing.

Fig. 2: A Virtex-7 FPGA on an ADC/DAC signal board<sup>1</sup>

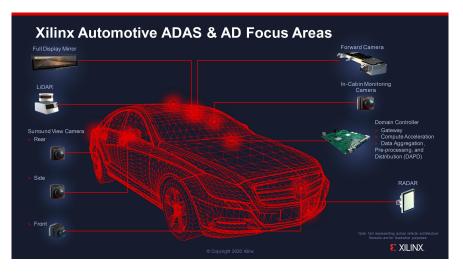

While SoCs like the Snapdragon 888 and other ICs are not intended to be physically changed after manufacturing, FPGAs allow for design flexibility and provides the opportunity to change how sections in a system work without introducing subsequent cost, delays, or design risk. For example, because FPGAs excel in processing digital signals quickly, one common application is machine vision. An FPGA projecting a back-up camera onto the rear-view mirror of a self-driving car can be modified to reduce latency and comply with new government standards simply through a software update. Conversely, this flexibility is almost impossible with a microprocessor, as any drastic changes would ultimately result in a complete redesign.

This optimized behavior is possible due to one key point – FPGAs operate in parallel. Normally, a processor must load in instructions in a linear fashion, even for simple tasks such as multiplying or shifting bits. Each instruction must be evaluated in order before the CPU can move onto the next one. This is fine under normal use, but in real-time applications where latency must be as low as possible, having to wait for the AC to activate before the brake pedal can be used is unacceptable. In contrast, an FPGA can execute multiple complex operations simultaneously — with a 10-element matrix, a designer can implement 10 signal/data pipelines to use in parallel. While a microprocessor has sequential processing, an FPGA's concurrent processing allows it to achieve better optimization and a more deterministic latency than even a processor running an RTOS.

In more nuanced terms, the flexibility from an FPGA allows a designer to decide which operations occur at any given clock cycle. Even though FPGAs are clocked much slower than CPUs (100 MHz vs. up to 4 to 5 GHz), given the right design, FPGAs can become much more optimal than even the fastest CPUs. For example, instead of only being able

<sup>&</sup>lt;sup>1</sup> The example FPGA ADC/DAC board used.

<sup>&</sup>lt;sup>2</sup> Xilinx's automotive system is discussed in this press release.

Fig. 3: Example of how an FPGA can excel as a DSP for self-driving cars<sup>2</sup>

to multiply two numbers at every cycle with a CPU, a designer can use all 10 pipelines to multiply 20 numbers for every single cycle - 1/10th the time it would take with a traditional CPU, assuming that the CPU is never interrupted by another instruction. Because an FPGA has very high determinism (in that we know exactly when each instruction will execute), we can rest easy knowing that the FPGA will never be unintentionally interrupted and continue to perform at a consistently high threshold.

**Important:** If you are coming from a traditional programming background, this is an especially crucial point. You are most likely accustomed to coding in sequential order, so always consider concurrency when working with FPGAs!

Fig. 4: A dual-core CPU vs. multi-channel FPGA<sup>3</sup>

<sup>&</sup>lt;sup>3</sup> More about FPGA computational performance can be found in this article.

# 1.3 What's Inside an FPGA?

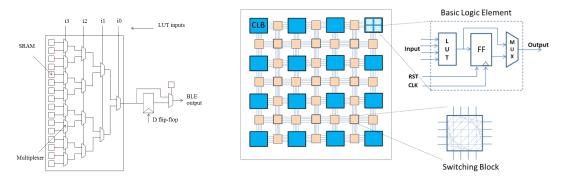

While a software engineer writes linear high-level code to become compiled into low-level assembly instructions, a hardware designer does not have a compiler; instead, they manipulate much lower-level discrete digital components like LUTs, registers, etc. Again, this is important to remember moving forward — while programmers write software code, FPGA designers 'code' physical hardware present on the FPGA itself.

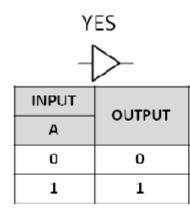

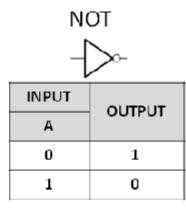

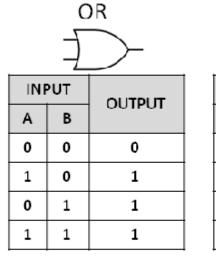

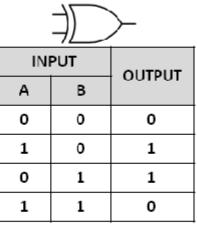

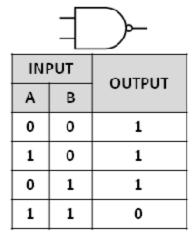

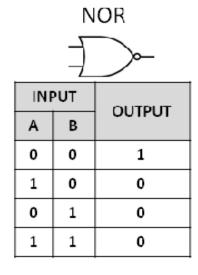

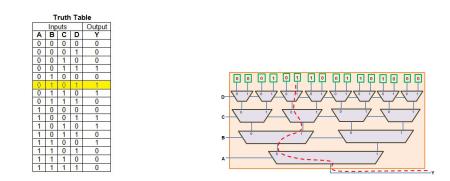

The smallest component on an FPGA is the simple logic gate. Of course, discrete logic gates do not physically exist inside an FPGA — instead, FPGAs calculate Boolean algebra using look up tables (**LUTs**) as truth tables, where each LUT can calculate any Boolean algebra equation based on the number of inputs. A typical FPGA will have thousands of three, four, and five-input LUTs. More about Boolean algebra and logic gates here.

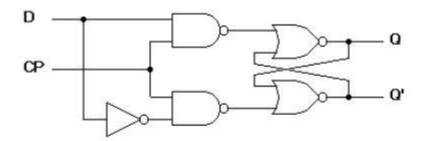

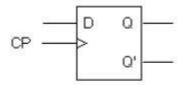

By combining multiple logic gates together, we can create truth tables that achieve more complicated functions. One of the most common examples is a **D flip-flop**, a logic component that changes the output Q based on the input D. The FF stores the current value on the D data line, essentially acting as a basic memory cell. FFs use sequential or registered logic, meaning that it operates based on the regular transitions of a clock, driven by the clock input line (>). FFs register data from D to Q on a clock's rising (or falling) edge, or when the clock transitions from 0 to 1 (or 1 to 0). With multiple flip-flops (or registers in this case) all acting as data storage elements, they collectively store the current state of the entire FPGA, including counters, state machines, and evaluations of other components. If an FPGA only had LUTs without any FFs, the FPGA would have no memory, forced to immediately evaluate all changes on any inputs and preventing any saved programs from working (meaning that our multiplication example from before would no longer function).

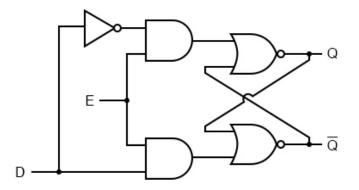

In a similar manner, a **gated D latch** is a simpler non-clocked flip-flop that is also used to store state information. A D flip-flop uses a clock signal to transfer data, while a latch simply checks an E enable input line. As before, input D is the data input line, containing the value to transfer to output Q (or Q bar, the opposite of Q). Q only receives the value on D when Enable is HIGH or 1 - when E is 0, output Q is considered 'latched' and will not change regardless of input D.

**Note:** Latches are often created unintentionally from incomplete assignments, so beginners are not advised to use them until they have significant FPGA debugging experience.

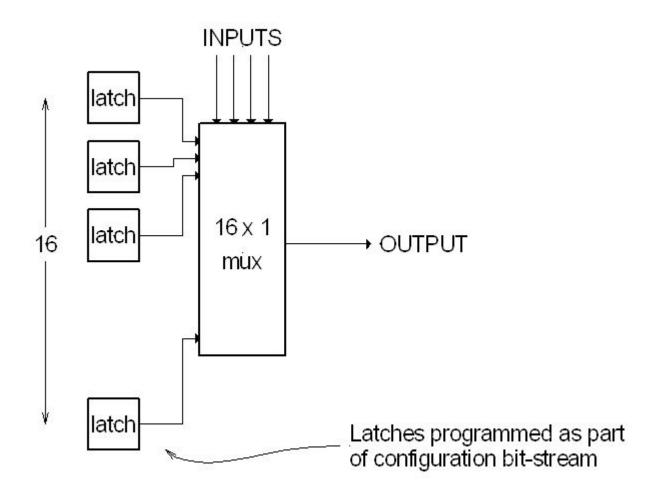

From an overarching perspective, an n-bit LUT is implemented as a  $2^n \times 1$  memory component. In other words,  $2^n$  SRAM latches hold the value of each LUT input combination, creating a larger general purpose truth table. Each latch is controlled by a  $2^n \times 1$  multiplexer, or **mux**, which is a simple logic component that chooses which of its multiple inputs to transfer to its output line. LUT inputs into the mux control determine which latch values are passed to output Q. For example, 16 latches store multiple values in memory and feed into a 16 by 1 mux. The mux also receives control inputs that determine which latch is pushed to the output.

For example, given a 4-input truth table with 16 rows, for the input ABCD = 0101, the output Y will be  $1^7$ .

LATCH/FLIP-FLOP. The Mediterranean Journal of Electronics and Communications, 8(4).

<sup>7</sup> More about LUTs here.

<sup>&</sup>lt;sup>4</sup> From Abels, S. G., & Khisamutdinov, E. F. (2015). Nucleic Acid Computing and its Potential to Transform Silicon-Based Technology. DNA and RNA Nanotechnology, 1(open-issue), 13-22.

<sup>&</sup>lt;sup>5</sup> More about flip flops and their diagrams are here.

<sup>&</sup>lt;sup>6</sup> From Abdel-Lattif, G. Y., Rehan, S. E., & Abdel-Fattah, A. F. I. (2012). OPTIMIZED SINGLE-ELECTRON NAND-BASED D-

AND

OUTPUT

INPUT

В

А

XOR

NAND

Fig. 5: Summary of common logic gates/truth tables<sup>4</sup>

(a) Logic diagram with NAND gates

# (b) Graphical symbol

| QD | Q(t+1) |

|----|--------|

| 00 | 0      |

| 01 | 1      |

| 10 | 0      |

| 11 | 1      |

# (c) Transition table

Fig. 6: Summary of a D flip flop<sup>5</sup>

| Е | D | Q     | Q     |

|---|---|-------|-------|

| 0 | 0 | latch | latch |

| 0 | 1 | latch | latch |

| 1 | 0 | 0     | 1     |

| 1 | 1 | 1     | 0     |

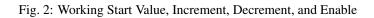

Fig. 7: Summary of a D latch<sup>6</sup>

Fig. 8: Abstracted block diagram of a look-up table

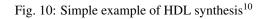

A flip-flop then stores the LUT's output. One last multiplexer decides, based on the given configuration, whether the output receives the value from the flip-flop or directly from the LUT itself. As a whole, all components make up a single **configurable logic block** (**CLB**). Like the introductory video, these logic blocks are routed togther using switching blocks to finally make up the entire FPGA floorplan<sup>8</sup>.

### 1.4 The Basics of Hardware Emulation and HDLs

As we have discussed at length, FPGAs provide an unparalleled combination of performance and flexibility that rivals even the most expensive processors (of course, industry-grade FPGAs cost quite a bit too). This reprogrammability allows FPGAs to excel at one of their most interesting applications — **hardware emulation** or the method of copying the behavior of another hardware sample. Referring to our Apple M1/Qualcomm 888 example, instead of manufacturing new designs on the assumption that they will work 100% of the time, most if not all semiconductor companies first use FPGAs to emulate their chips. Hardware emulation allows these manufacturers to debug their designs in simulated but realistic conditions before undertaking the extreme cost of mass fabrication. By chaining multiple FPGAs together (sometimes up to the scale of entire rooms for one chip alone), these companies are able to logically simulate even the most complex integrated circuits in real time, testing both hardware performance and software compatibility. Modern GPUs and CPUs have billions of transistors, so ultimately hardware emulation is and will continue to be an essential part in the semiconductor industry.

Hardware emulation is achieved through a number of steps. First, the design is created from **HDL** code, also known as a hardware description language. Similar to traditional programming languages like C or Python, an HDL like Verilog or VHDL instantiates the FPGA's physical hardware using digital code. HDLs execute instructions in parallel, while software languages operate in sequential order. Designs are then **synthesized**, wherein the human-understandable code is converted in a **netlist** of connected logic gates or flip-flops. Essentially, synthesis acts the same as compiling software code to machine assembly code.

Place and route (**P&R**), or implementation, is a set of multiple procedures in which the list of nets is physically placed and mapped to the FPGA's resources. Implementation creates a roadmap where each element can be placed onto the

<sup>&</sup>lt;sup>8</sup> FPGA floorplan from this info page.

<sup>&</sup>lt;sup>9</sup> More about NVIDIA's emulation lab in this blog post.

<sup>&</sup>lt;sup>10</sup> Details about the FPGA design flow here.

Fig. 9: An entire room-scale Cadence Tigris emulator<sup>9</sup>

module and2 (c, b, a); output c; input a,b; assign c = a&b; endmodule

# AND gate using Verilog

# Synthesized AND gate

FPGA chip. At the end, the software will output a **bitstream** that designers can program onto the FPGA for further testing. Both synthesis and implementation are typically done with first-party software, although synthesis can be completed with third-party alternatives.

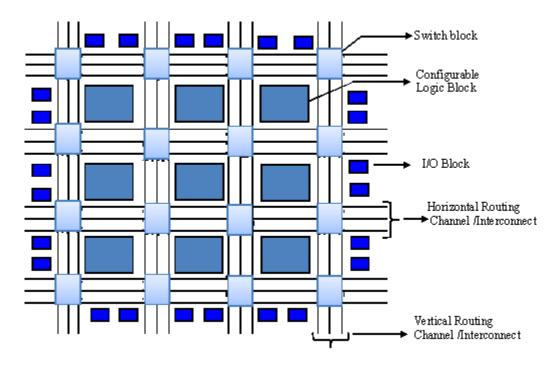

Fig. 11: Simple example of  $P\&R^{11}$

Finally, the tasks of **simulation** and **verification** provide useful debugging methods along the entire development process. Verification is a multi-stage procedure from writing a testbench or set of tests in HDL code that checks the design against a given specification to testing for timing concerns. Behavioral simulation is one aspect of verification that simulates an environment based on the testbench and outputs relevant signal waveforms. Do not worry if you have little experience with reading waveforms or using an oscilloscope, as we will be explaining our simulation tests in every example project we provide using Vivado's ModelSim. This article will not go into SystemVerilog and UVM, as that is outside the scope of this entire project.

Fig. 12: Simulating an 8-bit binary counter

Of course, going through the entire process from synthesis to bitstream for every single hardware component is timeconsuming, especially if you are repeatedly working with the same FPGA. It would more efficient and easier to first create the infrastructure first in the form of an **emulation environment**. This would include peripherals like the board memory or PCIe pinout, which never change between designs. After all, if you end up working with the same board, why start from scratch for every project? A premade environment allows us to get a running start for every future project onwards, which is why setting up such an environment is our first example project.

<sup>&</sup>lt;sup>11</sup> Venugopal, N., Shobana, V., & Manimegalai, R. (2014, January). Analysis of optimization techniques in FPGA placement. In 2014 International Conference on Computer Communication and Informatics (pp. 1-5). IEEE.

**Note:** Don't worry if you don't have access to a physical FPGA board — 90% of design work is done in simulation anyways!

After the environment is completed, we will continue to guide you through creating and simulating a device under test (**DUT**), letting you emulate everything from a simple counter to a complex SoC.

**Important:** Jump *here* to get started with your environment. Otherwise, continue to the next page for a deeper introduction into the hardware.

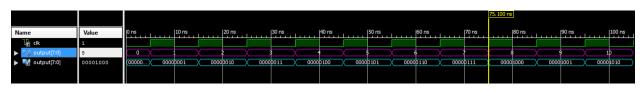

What is a real-world example of hardware emulation? One interesting application that has evolved in the last few years is the MiSTer project, an open-source design that emulates old video game consoles using nothing more than a small FPGA board. Using the same principles as software emulation, the MiSTer project emulates multiple reversed-engineered consoles on a single Altera Cyclone FPGA, opening the opportunity for a home arcade at a fraction of the price. Instead of paying hundreds of dollars for a new and working Nintendo Famicom Disk System, which was never released in the West, or use software emulation to run code in a similar fashion, the FPGA board can instead emulate the console hardware itself and play every game that was ever released with the same level of performance and compatibility. Of course, since FPGAs are flexible, an FPGA can reconfigure itself through LUTs to emulate other hardware. This means that different console cores from Atari to Pac-Man can be swapped out at any time, again illustrating the versatility of FPGAs and serving as a good example for our emulation environment project. By building up the proper infrastructure, it would become easy in the future to swap in different DUTs like the MiSTer cores for testing and debugging, similar to standard industry practices in the semiconductor field. All without even touching the original hardware.

Fig. 13: Emulating an NES game console on an FPGA<sup>12</sup>

<sup>&</sup>lt;sup>12</sup> More about the NES FPGA project here.

# **1.5 Quick Definitions and Acronyms**

- IC [Integrated Circuit] Collection of electronic components on a single unit, typically made from silicon, also known as a chip.

- FPGA [Field Programmable Gate Array] ICs designed to be configurable by engineer after manufacturing.

- ASIC [Application Specific Integrated Circuit] Highly specialized ICs dedicated to one specific application.

- SoC [System on a Chip] IC that hosts an entire computer system by itself.

- **P&R** [Place and Route] Process by which logic components are placed onto an FPGA and connected/routed together.

- DUT [Device Under Test] Any electronic part currently being tested, through emulation in our case.

- **IP** [Intellectual Property] Commonly used electronic parts abstracted as logic blocks, provided by external companies (not the same as a patent).

- AXI [Advanced eXtensible Interface] Communication standard that allows chip components to send signals to each other.

- MIG [Memory Interface Generator] Xilinx IP that allows an FPGA to read/write into DDR memory.

- **DDR SDRAM** [Double Data Rate Synchronous Dynamic Random-Access Memory] Volatile memory IC typically used to store information that is lost when power is lost, common interfaces are DDR3 and DDR4.

- **PCIe** [Peripheral Component Interconnect Express] Communication network that allows an FPGA to control peripherals/communicate with a host PC.

- TLP [Transaction Layer Packets] Data payloads that peripherals send through the PCIe bus.

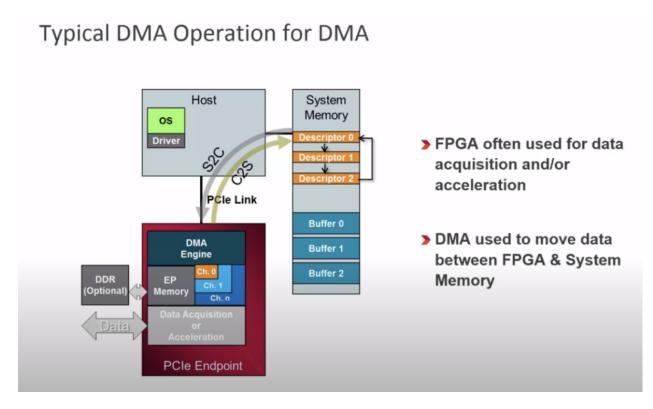

- **DMA** [Direct Memory Access] Xilinx IP that allows AXI peripherals to directly access memory without the help of the processor.

- **ROM** [Read Only Memory] Flash memory that cannot be modified afterwards.

# 1.6 References

#### CHAPTER

# **AXI PROTOCOL OVERVIEW**

### 2.1 The AXI Protocol

When building your first block diagram or reading the documentation of Xilinx's IP cores, you may notice one thing in common – they all use the AXI protocol. This article will provide a brief explanation about what AXI is and how it functions.

The *Advanced eXtensible Interface*, or **AXI**, protocol is a royalty-free communication standard developed by ARM, a prolific system-on-chip (SoC) company, as part of the AMBA (Advanced Microcontroller Bus Architecture) standard. You can find more information about AMBA and its other protocols (such as AHB or APB) here.

Essentially, the AXI protocol outlines the process by which on-chip components can communicate with each other using signals, usually involving a master and slave device. By standardizing this protocol, we can ensure every peripheral and IP core present on an FPGA will be able to talk to each other, creating a cohesive system (rather than a scattered collection of cores).

There are three types of AXI4 interfaces (defined by AMBA 4.0):

- Full AXI4 High-performance communication, using memory-mapped addresses (more here).

- AXI-Lite Lightweight and simple memory-mapped interface, used for single transaction communication.

- AXI4-Stream 'Direct' device communication, removing the need for addresses and allowing for maximum data transfer.

For the remainder of this article and throughout our projects, we will mainly focus on Full AXI4 for the best performance-cost ratio.

### 2.2 AXI Reads and Writes

| Memory Addresses                                   |                |               |  |

|----------------------------------------------------|----------------|---------------|--|

| Example of how AXI can control devices using addr  | esses.         |               |  |

| Both pure data and commands (like toggling an LED) | can be sent on | the data bus. |  |

| Adda                                               |                | _             |  |

| Addres                                             | s Purpose      |               |  |

| 0x0000                                             | 0 Config       |               |  |

| 0x1000                                             | 0 LED1         | 7             |  |

| 0x2000                                             | 0 DDR Reg      |               |  |

AXI4 allows for multiple data transfers over a single request, allowing for greater data bandwidth in the scenario where large amounts of data must be transferred to/from specific addresses. This multi-transfer request is also known as a *burst*.

All AXI communication is with respect to memory addresses, which each have a specific purpose defined by the RTL and top module.

Three burst types are supported - **FIXED**, **INCR**, and **WRAP**. Each one alters the transfer address in a specific way, allowing for optimal transfers in different situations. For example, a FIXED burst sets every beat to have the same address, which is useful for memory transfers from the same repeated location.

In general, burst addressing specifies where each read or write should be performed in which addresses. Each burst type is as follows<sup>1</sup>:

Fig. 1: AXI Bursts

AXI4-Lite has no burst protocol (only sending one piece of data at a time) while AXI4-Stream acts as a single unidirectional channel for unlimited data flow between a master and slave, removing the need for addresses.

# 2.3 AXI4 Connections and Channels

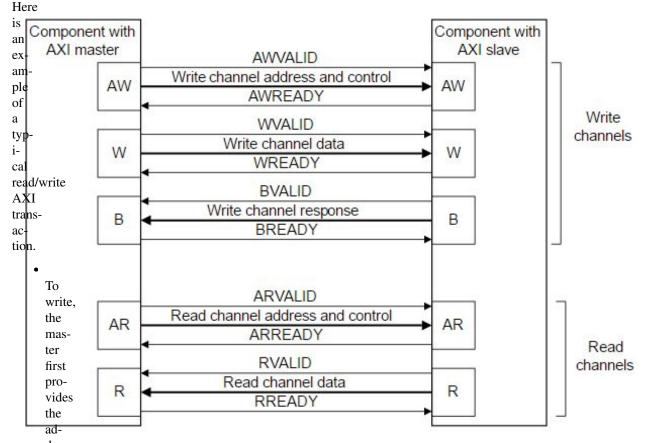

In its most basic configuration, the AXI protocol connects and facilitates communication between one master and one slave device. As expected, the master initiates and drives data requests, while the slave responds accordingly. This communication, or transactions as we will now refer to, occurs over multiple channels, each one dedicated to a specific purpose.

The sender must always assert a VALID signal before the receiver and keep it HIGH until the handshake is completed. By using handshakes, the speed and regularity of any data transfer can be controlled.

There are five channels, each one transmitting a data payload in one direction. Each channel implements a handshake Fig. mechanism, wherein the sender drives a VALID signal when it has prepared the payload for delivery and the receiver drives a READY signal in response when it is ready to receive the data. The data transfer is also known as a *beat*. AXI Hand-

The five AXI4 channels are as follows:

- Write Address channel (AW): Provides address where data should be written (AWADDR)

- Can also specify burst size (AWSIZE), beats per burst (AWLEN + 1), burst type (AWBURST), etc.

- AWVALID (Master to Slave) and AWREADY (Slave to Master)

- Write Data channel (W): The actual data sent (WDATA)

- Can also specify data and beat ID

- Sender will always assert a finished transfer when done (WLAST)

- WVALID (Master to Slave) and WREADY (Slave to Master)

- 'Write Response channel (B): Status of write (BRESP)

- ' BVALID (Slave to Master) and BREADY (Master to Slave)

- ' Read Address channel (AR): Provides address where data should be read from (ARADDR)

'Can also specify burst size (ARSIZE), beats per burst (ARLEN + 1), burst type (ARBURST), etc. ARVALID (Master to Slave) and ARREADY (Slave to Master)

' Read Data channel (R): The actual data sent back

shake Pro-

to-

col

<sup>&</sup>lt;sup>1</sup> AXI example images used from Wikimedia Commons and the AXI Article.

' Can also send back status (RRESP), data ID, etc. Sender will always assert a finished transfer when done (RLAST) RVALID (Slave to Master) and RREADY (Master to Slave)

dress

(0x0)

to write to, as well as the data specifications (4 beats of 4 bytes each, data type of INCR). Both the master and slave then exchange a handshake for verification.

The master then prepares and writes the actual data payload to send over the

| chan-                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nel                                                                                                                                                             |

| (0x10,                                                                                                                                                          |

|                                                                                                                                                                 |

| 0x11                                                                                                                                                            |

| 0x12,                                                                                                                                                           |

| and                                                                                                                                                             |

| 0x13),                                                                                                                                                          |

|                                                                                                                                                                 |

| again                                                                                                                                                           |

| us-                                                                                                                                                             |

| ing                                                                                                                                                             |

| a                                                                                                                                                               |

|                                                                                                                                                                 |

| hand-                                                                                                                                                           |

| shake                                                                                                                                                           |

| to                                                                                                                                                              |

| ver-                                                                                                                                                            |

|                                                                                                                                                                 |

| ify                                                                                                                                                             |

| the                                                                                                                                                             |

| trans-                                                                                                                                                          |

| fer.                                                                                                                                                            |

|                                                                                                                                                                 |

| The                                                                                                                                                             |

| mas-                                                                                                                                                            |

| ter                                                                                                                                                             |

| will                                                                                                                                                            |

|                                                                                                                                                                 |

| sig-                                                                                                                                                            |

| nal                                                                                                                                                             |

| the                                                                                                                                                             |

| end                                                                                                                                                             |

|                                                                                                                                                                 |

| of                                                                                                                                                              |

| the                                                                                                                                                             |

| uic                                                                                                                                                             |

|                                                                                                                                                                 |

| pay-                                                                                                                                                            |

| pay-<br>load                                                                                                                                                    |

| pay-<br>load<br>to                                                                                                                                              |

| pay-<br>load                                                                                                                                                    |

| pay-<br>load<br>to<br>the                                                                                                                                       |

| pay-<br>load<br>to<br>the<br>slave                                                                                                                              |

| pay-<br>load<br>to<br>the<br>slave<br>us-                                                                                                                       |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing                                                                                                                |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing                                                                                                                |

| pay-<br>load<br>to<br>the<br>slave<br>us-                                                                                                                       |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.                                                                                                      |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing                                                                                                                |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.                                                                                                      |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave                                                                                      |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-                                                                               |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds                                                                     |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-                                                                               |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds                                                                     |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a                                                        |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-                                                |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus                                         |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-                                                |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus<br>of                                   |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus<br>of<br>the                            |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus<br>of<br>the<br>write                   |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus<br>of<br>the<br>write<br>and            |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus<br>of<br>the<br>write                   |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus<br>of<br>the<br>write<br>and<br>whether |

| pay-<br>load<br>to<br>the<br>slave<br>us-<br>ing<br>WLAST.<br>The<br>slave<br>re-<br>sponds<br>with<br>a<br>sta-<br>tus<br>of<br>the<br>write<br>and            |

•

successful or а failure (all OKAY in this case) and finishes the entire transaction with another handshake.

#### Fig. 3: A typical AXI Write transaction

- To read, the master first provides the first address to read from (0x0), as well as the data specifications (4 beats of 4 bytes each, data type of INCR). The usual handshake occurs.

- The slave then provides the actual data payload, as well as the status of each beat (all beats are OKAY). The slave will signal the end of the payload to the master using RLAST. As we can see, what was written to the specified addresses was the same as what was read back.

#### Fig. 4: A typical AXI Read transaction

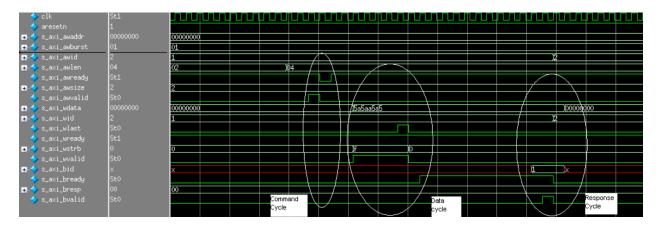

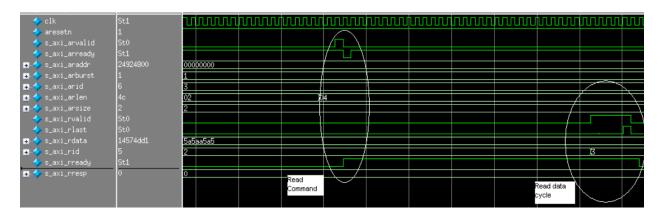

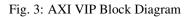

We can also get an idea about what an AXI read and write cycle would look like in simulation through the 7 Series MIG documentation (UG586). As we can see, an AXI write consists of a command cycle (define address and burst length), data cycle (putting the data payload over the channel), and a response cycle (checking if the data was received). The master defines the payload specifications and writes the actual data payload (5a5aa5a5 at address 00000000). The slave toggles s\_axi\_bvalid, exchanging a handshake that signifies the transfer was successful.

Subsequently, an AXI read consists of a read command cycle (again, defining the address to read from, burst length, etc.) and a read data cycle (receiving the data from the requested address). The master specifies the address (00000000) and other payload specs, receives the data payload from the slave (5a5aa5a5), and exchanges a final handshake by toggling s\_axi\_rlast to complete the transfer.

Fig. 5: AXI Write Cycle in Simulation

Fig. 6: AXI Read Cycle in Simulation

# 2.4 AXI Interconnect vs. SmartConnect

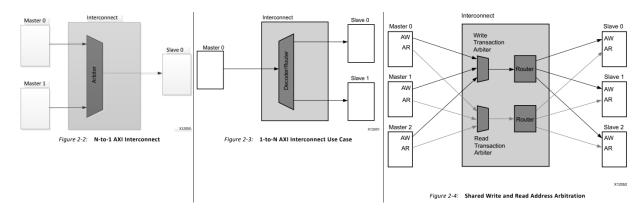

AXI is a very flexible standard in that it only outlines the interface itself, never requiring a designer to memorize multiple configurations for every scenario. This characteristic is exemplified with the introduction of the AXI Interconnect IP.

The AXI Interconnect IP is similar to an operating system in that both mediate data and resource transactions between two independent entities. The Interconnect IP is made up of a combination of arbiters, decoders/routers, multiplexers, and other logic elements that seamlessly adapts to any AXI system, whether it be a multi-master system connected to one slave, a multi-slave system connected to one master, or multiple masters connected to multiple slaves (up to 16 each).

Fig. 7: AXI Interconnect Configurations<sup>2</sup>

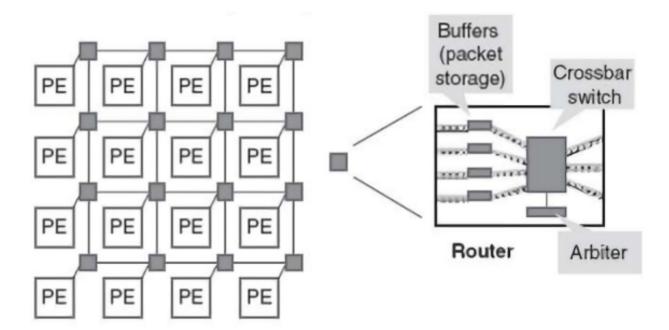

The AXI Interconnect is also known as a network-on-chip (NoC). There are many technical details about NoCs that we will not go into here, such as topology and routing strategies, but the only characteristic to keep in mind is that NoCs use packets, not wires, to route data from the source to the destination. While traditional Verilog instantiates connections between modules as wires and sends electrical signals as communication, NoCs like the Interconnect or SmartConnect utilize the AXI protocol to route signals and data payloads from the master to the appropriate slave device. The NoC architecture has multiple routers connected by wires or links with an array of processing elements or PEs built on a mesh topology. This creates a scalable architecture that has a higher bandwidth than connecting each module individually.

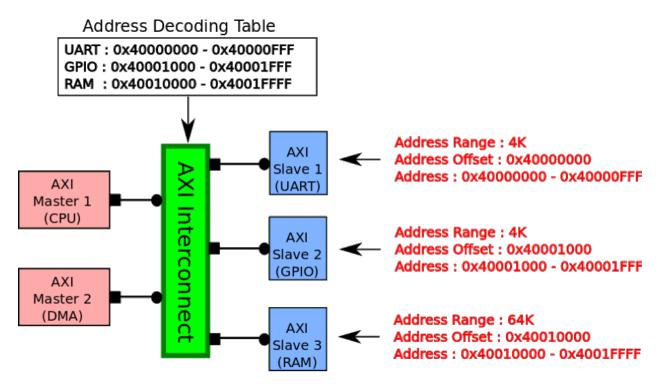

For a multi-master/slave system, the Interconnect will contain multiple arbiters and routers so that each write and read channel has a dedicated connection between masters and slaves — by doing this, both reads and writes can occur simultaneously. This is also known as an **AXI Crossbar** core. A typical Interconnect transaction would occur in this manner:

- As always, the master first provides the address for a write transfer onto the AW channel. The write transaction arbiter decides which master can monopolize the Interconnect Write channel and sends the master's address to the router.

- Using a preallocated address decoding table, the router then decodes the given address and selects the proper slave to write the address to. The typical AXI write transaction then commences, with an Interconnect multiplexer mediating a data transfer between master and slave.

- At the same time, another master can provide a different address to read from on the AR channel. The read transaction arbiter can also decide which master monopolizes the Interconnect Read channel, sending that master's address to a different router.

<sup>&</sup>lt;sup>2</sup> AXI Interconnect documentation from Xilinx here.

<sup>&</sup>lt;sup>3</sup> From Sudeep Pasricha (Colorado State), Nikil Dutt (UC Irvine) "On-Chip Communication Architectures", Morgan Kaufmann, 2008

Fig. 8: AXI Interconnect NoC topology<sup>3</sup>

• This second router also decodes the given address and selects either the same or a different slave to read from. An AXI read transaction then starts with another Interconnect multiplexer as a mediator.

The Interconnect IP works on a round-robin basis, wherein the read and write channel will alternate for access if multiple masters are trying to write to/read from the same slave. Since the DDR protocol allocates a few clock cycles between reads and writes, the IP cannot immediately switch channels. Because slaves can queue multiple transactions and this round-robin schedule allows for out of order transfers (a slave device can respond to a master whenever), a deadlock risk emerges. Deadlock is a scenario where a transfer #1 cannot fully complete while transfer #2 is running. To finish, #2 requires transfer #1 to complete first, creating an endless loop that is never resolved. You can read more about the Dining Philosophers Problem here.

From the Xilinx's Interconnect Documentation<sup>2</sup>, we can see how a deadlock situation can form:

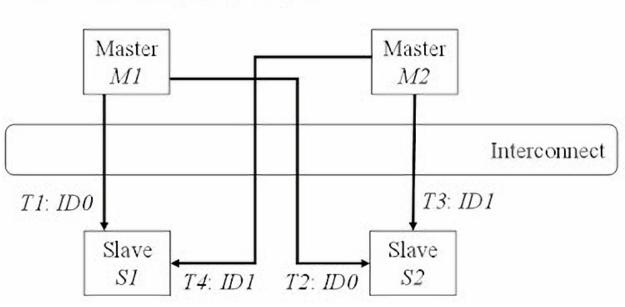

- 1. Master M1 reads from Slave device S1 using ID0.

- 2. Master M1 then reads from Slave device S2 using the same ID thread ID0.

- 3. Master M2 then reads from Slave device S2 with a different ID ID1.

- 4. Master M2 then reads from Slave device S1 using the same ID thread ID1.

- 5. Slave *S1* responds to Master *M2* first. It is allowed to respond to *M2* before *M1* first, since the two Masters have different IDs. However, the AXI Crossbar cannot pass the response to *M2* because Master *M2* must first receive its response from Slave *S2*.

- 6. Slave S2 responds to Master M1 first without re-ordering. But the AXI Crossbar cannot pass the response to Master M1 because M1 must first receive its response from Slave S1, resulting in a deadlock situation.

Helpfully, the AXI Interconnect IP already resolves this concern by mandating the "Single Slave per ID" rule, where generally only one master device can talk to any slave at any given time. With this in-order rule, the Read transaction in step 2 from M1 to S2 is stalled until S1 completes its response to M1. Similarly, the transaction between M2 and S1 in step 4 is stalled until S2 completes its response to M2. This is important to keep in mind as the AXI protocol itself

<sup>&</sup>lt;sup>4</sup> The example of Interconnect Addressing from Mohammadsadegh Sadri, PhD, can be found in this post.

Fig. 9: AXI Interconnect Address Decoding Table<sup>4</sup>

has no in-order check between Read and Write transactions, meaning that deadlock can occur elsewhere, especially when combining multiple Interconnects and SmartConnects together.

The Interconnect also can update AXI3 interfaces to AXI4, perform bus-width conversion, use input/output FIFOs and register slices to break down timing paths, and convert between different clock domains. Simply put, the Interconnect IP is a versatile core that allows a designer to utilize the AXI protocol to its fullest extent without diving deep into the technical minutiae.

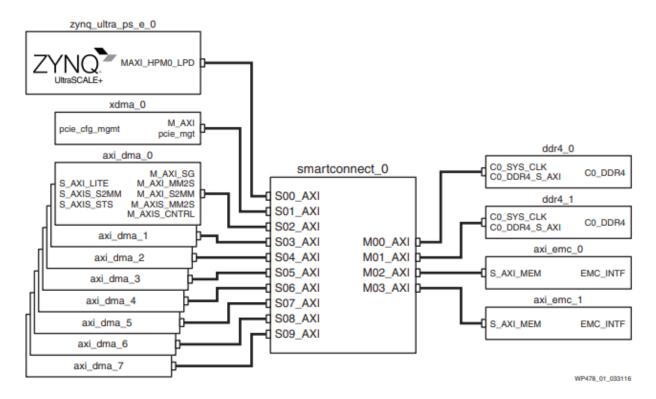

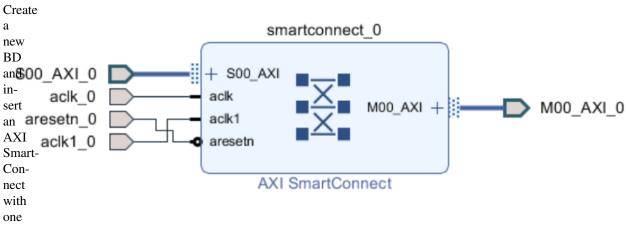

However, at the time of writing, the AXI Interconnect v2.1 core has been obsoleted by the new AXI SmartConnect IP. The SmartConnect operates on the same AXI4 principles of the Interconnect IP, providing similar performance with better optimization and a more streamlined experience. The AXI SmartConnect supports wider addressing and multi-threaded traffic along with a myriad of other benefits, so while Xilinx notes that pre-existing designs with the Interconnect v2.1 core do not need to upgrade, new designs are recommended to use the SmartConnect core moving forward. As such, our example designs will (almost) always use the SmartConnect IP as opposed to the older Interconnect. For more information, read the SmartConnect v1.0 documentation (PG247).

<sup>&</sup>lt;sup>5</sup> From Chou, H. M., Chen, Y. C., Yang, K. H., Tsao, J., Chang, S. C., Jone, W. B., & Chen, T. F. (2015). High-performance deadlock-free id assignment for advanced interconnect protocols. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(3), 1169-1173.

<sup>&</sup>lt;sup>6</sup> Read more about the SmartConnect IP in this white paper.

Issued Order:  $T1 \Rightarrow T2 \Rightarrow T3 \Rightarrow T4$

Fig. 10: An Interconnect deadlock situation<sup>5</sup>

Fig. 11: Example SmartConnect IP system<sup>6</sup>

# 2.5 AXI Verification IP

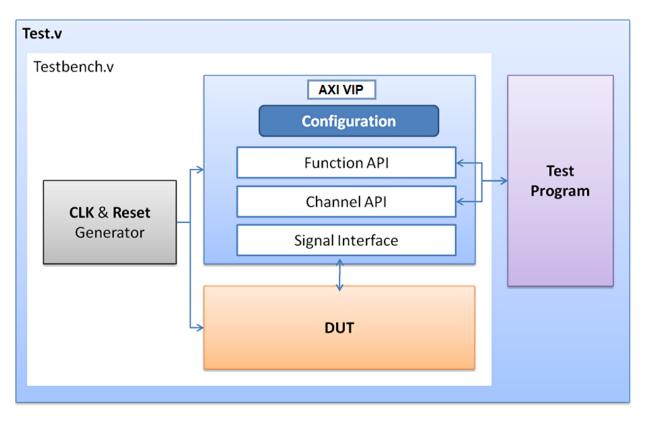

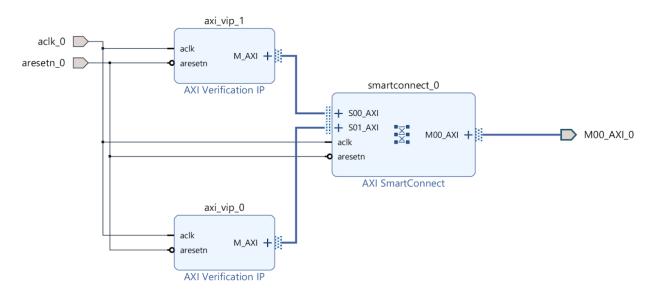

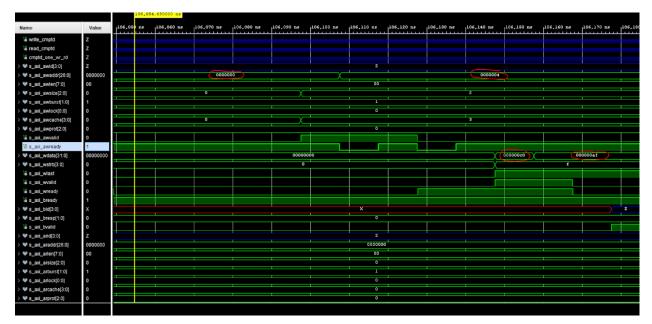

With some of our example designs, we have chosen to use the AXI Verification IP or **AXI VIP** as a test DUT. The VIP, which is provided by Xilinx, is a useful AXI4 core that allows us to debug our block designs and verify for expected behavior. It is the successor to the now obsolete AXI Bus Functional Model or BFM and all new designs will use the VIP moving forward, as the BFM is no longer available. The VIP can be dropped into any design and simulate a master, slave, and pass-through device (connecting a Slave to Master). It has one (optional) active LOW reset aresetn which is synchronous to aclk. This IP is mainly for simulation and is not synthesized. We will be using the VIP to verify data transactions in simulation and overall it is a good introductory method for catching errors in any custom AXI IPs (although the VIP suite is prone to missing some background transfer errors). While setting up the emulation environment and custom DUTs, we will be using the VIP to monitor and generate AXI transactions, as well as check for protocol compliance.

Fig. 12: Example AXI system with VIP<sup>7</sup>

# 2.6 References

<sup>&</sup>lt;sup>7</sup> More about AXI BFM architecure here (modified image).

#### CHAPTER

THREE

# LEGACY PCI AND PCI EXPRESS

Important: This article covers the PCI and PCIe buses. You can read about the specific AXI PCIe MM IP here.

# 3.1 Peripheral Component Interconnect

If you ever have built or looked inside a desktop, you may have noticed that a few boards connected to the motherboard all use the same interface. Since the 1990's, computers have utilized the *Peripheral Component Interconnect* or **PCI** bus to attach additional components and hardware devices via expansion slots. Modern examples include graphics processing unit (GPU) boards and enthusiast-grade sound cards.

Fig. 1: An example PCIe expansion card with x16 width

The PCI format allowed computer manufacturers to build and sell peripherals with a standardized format that was compatible with all motherboards and independent of any processor's requirements, essentially creating a plug-and-play system. The legacy PCI bus and its upgraded version **PCI-X** were eventually made obsolete by their successor

PCI Express, which we currently use in 2021.

Although many PCI peripherals are now integrated into the motherboard itself or available as external USB devices, the PCI bus remains relevant today due to its widespread usage among industrial and enthusiast fields. Since PCIe is backwards compatible with its older standards and builds upon PCI concepts, we will first examine the fundamentals of the legacy PCI standard.

# 3.2 PCI Overview and Background

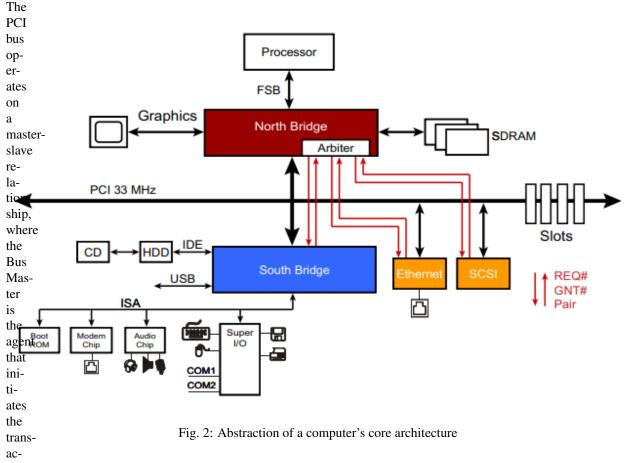

As a component bus (a bus is essentially communication between multiple components), all PCI concepts revolve around maintaining and processing transactions between peripherals and the processor (CPU). The PCI bus can be thought of as a traffic light, controlling the flow of data transactions between devices while other peripherals must wait for their turn to use the PCI bus. The external PCI bus works in tandem with the system bus, which allows internal computer components like the CPU or RAM to communicate with each other, and other external buses like the Universal Serial Bus, such as connecting a printer using an external USB cable.

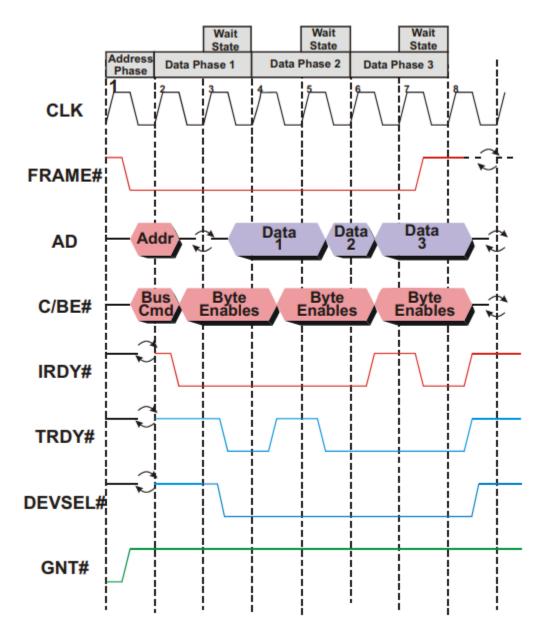

Legacy PCI is synchronous, in that all events occur on the edge of the computer's internal clock. A device would begin a data transaction and specify a start memory address, taking one clock cycle. Sending the data itself would take multiple cycles until the transaction finished, at which point the connection was ended.

tion (either the CPU or PCI boards) and the slave is the Target Device. Many modern devices have Bus Mastering capabilities, so an example transaction could involve a keyboard acting as a Bus Master to write data into main memory (the Target Device). This relationship can be further elaborated upon by looking at a motherboard's core architecture.

The northbridge or host bridge represents the core logic chip on the PC's motherboard that is 'north' of the central PCI bus. The northbridge interfaces between the CPU, system memory, the AGP (graphics) bus, and high-speed PCI bus. The northbridge's Bus Arbiter receives requests from all initiators (Bus Masters), decides which requester should monopolize the PCI bus, creates the transaction channel between the initiator and Target Device, and assigns a ready pin (GNT#).

The southbridge serves as the I/O controller hub, hosting all system I/O and connecting the PCI bus to external peripherals. It also provides system signals like reset, clock, and error reporting. From the southbridge, Bus Masters representing a peripheral can submit a request to use and monopolize the PCI bus. Each Bus Master has a pair of pins that they can request with (REQ#) or know when the bus is available to use (GNT#).

# 3.3 The Legacy PCI Bus Cycle

As mentioned before, Legacy PCI is synchronous as in events occur on clock edges. To illustrate this bus cycle better, we will examine a simple example of a typical bus transaction. Rising clock edges are marked with dotted lines whenever signals are driven or sampled.

Note: Signals with # are active LOW, signals without are active HIGH.

- CLK Edge 1 FRAME# (Bus Access) and IRDY# (Initiator Ready for data) are inactive, so PCI bus is idle.

- GNT# is active, showing that bus arbiter has selected this device to be the next initiator / Bus Master

- CLK Edge 2 FRAME# is asserted by the initiator, indicating that a new transaction has started.

- Initiator drives address and command for the transaction, other devices on bus will decode address to determine if they are being requested

- CLK Edge 3 Initiator indicates that it is ready for data transfer by asserting IRDY# to active low

- Arrow on AD bus shows that bus is undergoing turn-around cycle as ownership of signals changes (initiator drives address but also reads data on same pins)

- TRDY# is not driven low on the same edge as AD changing to avoid possibility of both buffers trying to drive a signal simultaneously, which can cause damage from shared signals

- CLK Edge 4 Device on bus has recognized requested address and has asserted DEVSEL# (device select) to proceed with transaction

- Also asserts TRDY# (target ready) to drive first part of read data onto AD bus

- Since both IRDY# and TRDY# are active at the same time, data begins transferring on that clock edge

- Initiator knows how many bytes will eventually be transferred, but target does not, so the target must check FRAME# to see if it is still asserted or not (will become inactive when done)

- CLK Edge 5 Target is not ready to deliver next set, so it de-asserts TRDY# for one clock cycle and enters a Wait State

- CLK Edge 6 Second data item is transferred, and since FRAME# is still asserted, the target knows that the initiator is still requesting for more data

- CLK Edge 7 Initiator forces a Wait State, allowing device to pause a transaction and either quickly fill or empty a buffer without stopping the request

- · Often very inefficient as they will both stall their current transaction and prevent bus access to other devices

- CLK Edge 8 Third data set is transferred, FRAME# is de-asserted so transaction is finished, at CLK edge 9 all control lines are turned off and bus becomes idle again

Fig. 3: Example Legacy PCI bus cycle

#### CHAPTER

#### FOUR

#### **DDR MEMORY AND SDRAM**

#### 4.1 What is RAM?

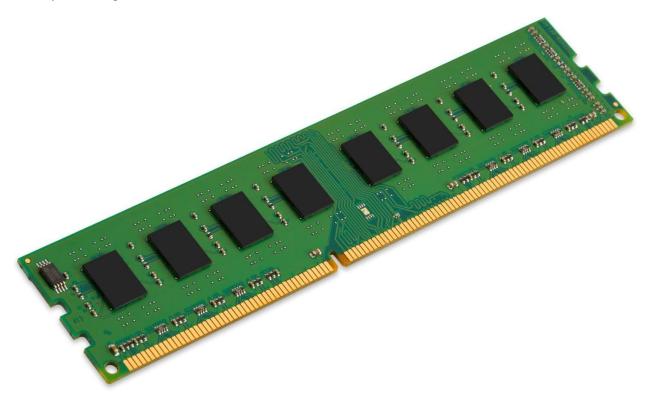

Inside any computer, phone, tablet, or other electronic device, it is almost guaranteed that there will be some sort of RAM inside that device. In fact, if you have ever looked inside a PC computer before, then you have most likely seen what a physical piece of RAM looks like. Below is an example of a DDR3 SDRAM component, and these can be purchased at most electronics stores (see Figure 1). The DDR stands for "Double-Data Rate", and the SDRAM stands for "Synchronous Dynamic RAM". These are just terms used to describe the process of how the RAM stores data, and they will be explained in more detail further down.

Fig. 1: Figure 1: Example DDR3 SDRAM Component

RAM stands for "Random-Access Memory", and like all memories, it's main purpose is to store information for future use. In your computer, for example, you should be able to check how much RAM is currently installed by going to your device settings. The more RAM that your computer has, the faster that it will be able to load programs and applications.

Almost all RAM components are "volatile" memory devices, which means that any stored data will be lost once the RAM loses power. Because of this, RAM is often used to store temporary data, such as program or application data. For more permanent storage of information, another type of memory such as "Read-Only Memory" (ROM) can be used instead. A good example of ROM is a CD disk, which is initially programmed with data (music, video, games, etc.) and is not meant to be overwritten (see Figure 2).

Fig. 2: Figure 2: Example of CD ROM

Most computers have both RAM and ROM components inside them, as RAM is needed for storing program/application data and ROM is needed for storing permanent instructions (i.e: boot-up instructions). They both have their own advantages and disadvantages, and so there is always a tradeoff between speed and volatility. While RAM components are generally much faster than ROM components, ROM has the ability to retain information even after power has been removed from the device.

# 4.2 Different Types of RAM

RAM can come in all shapes and sizes, but the two most common types of RAM are "Static RAM (SRAM)" and "Dynamic RAM (DRAM)". While both SRAM and DRAM are effective at storing temporary data, the main difference between them lies in how each of them store this data. SRAM is referred to as "static" because it is made up solely of transistors. DRAM, on the other hand, uses capacitors to store the data. Both have their own advantages and disadvantages, and so let's take a closer look at each type of RAM.

# 4.3 SRAM

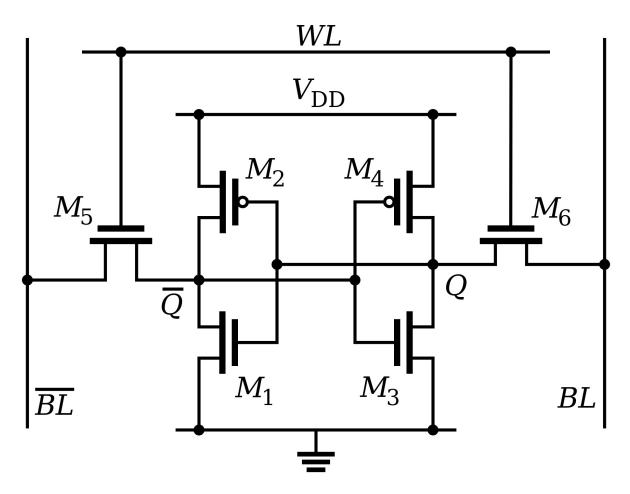

Looking at the figure below (figure 3), we can see what a typical SRAM cell configuration looks like. The parts labeled M1 through M6 are MOSFET transistors, the line labeled WL corresponds to the "Write Line", and the line labeled BL corresponds to the "Bit Line". The write line and the bit line are used simultaneously to control the read and write operations of the SRAM. For example, if we wanted to write a new bit value into this SRAM cell, we would simply place the desired bit value on the bit line (1 or 0), and then we would place a 1 on the write line to enable the write transaction.

Fig. 3: Figure 3: Typical SRAM Cell Configuration

The primary advantage of using SRAM components is that they are much faster than DRAM components. However, with the advantage of being faster, they are also much more expensive to manufacture. Therefore, SRAMs are typically

only used for small amounts of memory that really need that extra speed. For example, a standard use of SRAM is for your computer's cache memory, which stores frequently-used instructions and data for faster fetching by the CPU. Have you ever noticed that after you restart your computer, it takes slightly longer to load any given website? This is because your computer has information stored inside its cache that allows the website to load faster, and when you restart your computer, you are also clearing that cache memory.

# 4.4 DRAM

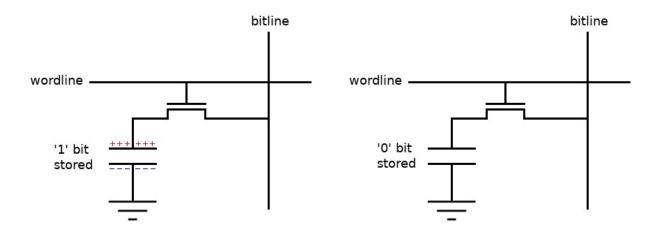

In comparison to SRAM components, DRAM utilizes capacitors in order to store memory. The typical configuration of a DRAM cell can be seen below in figure 4, and as you can see, the configuration appears to be much simpler than the SRAM cell. The bitline and the worldline are still present, and they are utilized in the same way as the SRAM cell. However, there are not nearly as many transistors required for the DRAM cell, which means that the cost to manufacture a DRAM component is far less than that of an SRAM component.

Fig. 4: Figure 4: Typical DRAM Cell Configuration

The fact that DRAM components are much cheaper than SRAM components make them a great choice for storing large amounts of data. For example, when you purchase a large piece of RAM like the illustration in figure 1, you are purchasing DRAM (the term "SDRAM" refers to Synchronous DRAM). While SRAM components like cache memory are typically in the kilobyte to low megabyte range, DRAM components can go all the way up to gigabyte range. The primary disadvantage of DRAM is that it is usually slower than SRAM, and this is due to the effects of using a capacitor. Over time, capacitors can begin to slowly discharge, and this can be very bad if it causes the stored data to be lost. In order to prevent this, DRAM components have to be constantly "refreshed", which essentially just means that the current data values have to be re-written into the capacitors.

# 4.5 The DDR SDRAM Protocol

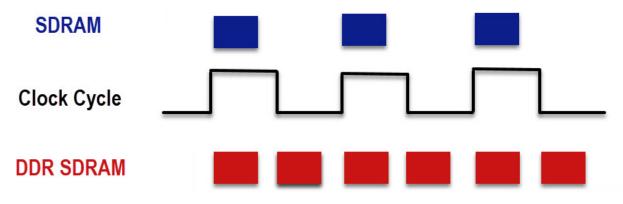

If you look back to our example in figure 1, you'll notice the specific memory part is called "DDR3 SDRAM". Well, now that we know what DRAM is, let's take a look at the rest of this name. First, let's look at the term "SDRAM". While this name may look similar to the Static RAM (SRAM) discussed earlier, it is actually referring to something very different. In a typical DRAM cell, there is no clock associated with the read and write transactions. However, digital electronics engineers are very fond of using clocks to keep everything synchronous in their designs, and so Synchronous DRAM (SDRAM) was created. This essentially means that read and write operations will only be processed on the rising edge of an associated clock.

Now that the read and write operations have been synchronized, a lot of the messiness has been cleaned up that could potentially occur from doing multiple asynchronous transactions. However, only sending data on one edge of a clock is rather slow, and it wastes time that could potentially be used for processing other transactions. Therefore, the Double Data Rate (DDR) protocol was created, and this process allows data to be sent on both the positive and the negative edge of an associated clock. This process can be seen below in figure 5.

Fig. 5: Figure 5: DDR SDRAM vs SDRAM Protocols

There have been many variations of the DDR SDRAM protocol, and the term "DDR3" refers to the third generation of this protocol. At this current time in 2021, DDR5 is the most current and up-to-date DDR protocol, and it was released in July of 2020. However, DDR3 and DDR4 are both still used widely in electronics today.

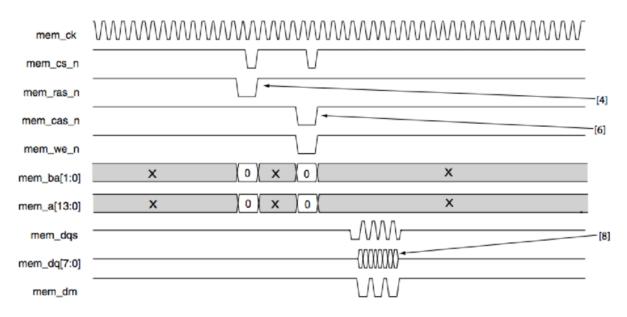

Specific information about timing, signals, resets, and more can all be found in the DDR3 SDRAM High-Performance Controller User Guide from Intel. For example, let's take a look at this DDR3 Timing Diagram seen below in figure 6.

At the top of this diagram is the memory clock, which is what the DDR memory device uses to clock its transactions. Then, right below the clock are the memory chip select signal, the row-address strobe signal, the column-address strobe signal, and the write enable signal. All four of these signals are used to set up or initialize the desired read or write transaction. After these signals come the memory bank bus and the memory address bus, and these point specifically to the memory location that you would like to read or write from. Finally, the memory strobe signal indicates when the data is being transferred, the data bus contains the specific data, and the memory data mask signal indicates which bytes of data should actually be transferred. For a greater description of these signals, see the attached "Table 4-6 DDR3 SDRAM Interface Signals" from the DDR3 SDRAM High-Performance Controller User Guide.

| Table 4–6. DDR3 SDRAM Interface Signals (Part 1 of 2) |               |                                                                                                                 |  |  |  |  |

|-------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Signal Name                                           | Direction     | Description                                                                                                     |  |  |  |  |

| mem_dq[]                                              | Bidirectional | Memory data bus. This bus is half the width of the local read and write data busses.                            |  |  |  |  |

| mem_dqs[]                                             | Bidirectional | Memory data strobe signal, which writes data into the DDR3 SDRAM and captures read data into the Altera device. |  |  |  |  |

| mem_dqs_n[]                                           | Bidirectional | Memory data strobe signal, which writes data into the DDR3 SDRAM and captures read data into the Altera device. |  |  |  |  |

| Table 4–6. DDR3 Sl   | Table 4–6. DDR3 SDRAM Interface Signals (Part 2 of 2) |                                                                      |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|

| Signal Name          | Direction                                             | Description                                                          |  |  |  |  |  |  |

| mem_clk (1)          | Bidirectional                                         | Clock for the memory device.                                         |  |  |  |  |  |  |

| mem_clk_n <i>(1)</i> | Bidirectional                                         | Inverted clock for the memory device.                                |  |  |  |  |  |  |

| mem_a[]              | Output                                                | Memory address bus.                                                  |  |  |  |  |  |  |

| mem_ba[]             | Output                                                | Memory bank address bus.                                             |  |  |  |  |  |  |

| mem_cas_n            | Output                                                | Memory column address strobe signal.                                 |  |  |  |  |  |  |

| mem_cke[]            | Output                                                | Memory clock enable signals.                                         |  |  |  |  |  |  |

| mem_cs_n[]           | Output                                                | Memory chip select signals.                                          |  |  |  |  |  |  |

| mem_dm[]             | Output                                                | Memory data mask signal, which masks individual bytes during writes. |  |  |  |  |  |  |

| mem_odt[]            | Output                                                | Memory on-die termination control signal.                            |  |  |  |  |  |  |

| mem_ras_n            | Output                                                | Memory row address strobe signal.                                    |  |  |  |  |  |  |

| mem_reset_n          | Output                                                | Memory reset signal.                                                 |  |  |  |  |  |  |

| mem_we_n             | Output                                                | Memory write enable signal.                                          |  |  |  |  |  |  |

# 4.6 References

# **CLOCKS, CLOCKING WIZARD, AND TIMING**

Note: This page is currently under construction.

### 5.1 Clocks and Clock Conversion

Square wave with 50% duty cycle, can be 0 or 1 Determines how fast the design will run, drives all sequential logic (flip-flops, RAMs, FIFOs) Can have multiple clock domains in a single FPGA

#### 5.2 Clock Tree

A dedicated input pin is used for clock signal, dedicated routing, logic used to minimize skew

Skew is difference in time between when it arrives at one FF to when it arrives at another FF, skew should be as small as possible

Clock tree network distributes the clock via dedicated routing signals to all FFs within the design

# 5.3 Multiple Clocks in an FPGA

Best to avoid multiple clocks for beginners

Usually only need different clocks if interfacing to some external component that requires it Ex. SDRAM, camera, special sensors Can use phase-locked loop (PLL), takes in reference clock to branch off into a different frequency

Typically use only one clock and Clock Enable signal Ex. UART has 19200 baud rate but don't need dedicated 19.2 kHz clock, just run a 50 MHz clock in intervals with counter

Never drive the clock of a FF off the output of another FF Use one central clock and parse through data with Clock Enable pulses Ex. input clock of 40 MHz, ADC runs of 10 Mhz, divide input signal by 4 and pulse once during output

# 5.4 Propagation Delay

Amount of time it takes for a signal to travel from a source to a destination Rule of thumb: signals can travel one foot of wire in one nanosecond Physical length of wires on board can be over a foot long, meaning that every portion of logic will take some finite delay time Propagation delay directly relates to sequential logic driven by a clock

Amount of time it takes from the output of one FF to travel to the second FF is the propagation delay The further apart or the more logic between the two FFs, the longer the delay, and the slower the clock is able to run Both FFs use the same clock, output of first FF at clock edge 1 should drive the second at clock edge 2 2 FFs that are 10 ns apart, a 50 MHz clock (20 ns period) will be fine while a 200 MHz clock (5 ns period) is not

FPGA timing analyzer will spot any timing errors Fix high propagation delay Slow down clock frequency Break up logic into stages through pipelining

Breaking up the logic between 3 FFs allows only half of the logic to be done between 2 FFs at a time Tools will have almost twice as much time to execute in a single clock cycle, also known as pipelining

# 5.5 Setup and Hold FF Time

Setup time - amount of time required for the input to a FF to be stable before a clock edge Hold time - minimum amount of time required for the input to a FF to be stable after a clock edge

Setup time, hold time, and propagation delay all affect FPGA design timing Minimum period of FPGA clock (and frequency where F = 1/T) can be calculated through tclk (min) = tsu + th + tp Generally, setup and hold time are fixed for FFs, so propagation delay is variable The more logic, the longer the propagation delay will be and the higher the clock period will be, leading to a slower frequency

If there are setup or hold time violations, the FF output is not guaranteed to be stable (could be 0, 1, or something else), also known as metastability Can check for metastability through placing and routing and timing analysis

### 5.6 Metastability Prevention

# 5.7 Clock Domain Crossing (CDC)

### LINUX DRIVERS, KERNEL PROGRAMMING, AND YOU

#### 6.1 What is a Driver?

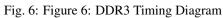

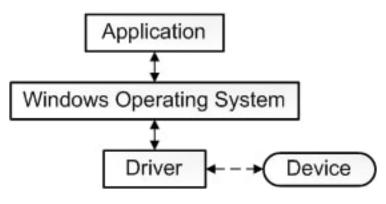

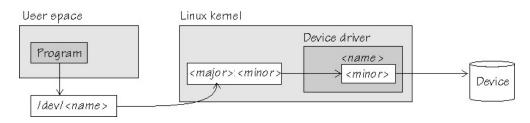

Software drivers play a critical role in how we use computers and electronics on a daily basis, yet most users never consider the complexity of driver development. As a very brief introduction, we will conceptualize a driver as any software component that lets the operating system or OS (such as Linux or Windows) communicate with an external device, like a keyboard. These devices can represent either physical hardware or other software tools. A driver allows user applications to interact and exchange data with other devices through the OS. For a more in-depth introduction to drivers and driver development, read this quick article from Microsoft here.

Device drivers are parts of the operating system that facilitate the usage of hardware devices via certain programming interfaces so that software applications can control and operate the devices. As each driver is specific to a particular operating system, you need separate Linux, Windows, or Unix device drivers to enable the use of your device on different computers (this is why a career in driver development and embedded systems is often lucrative).